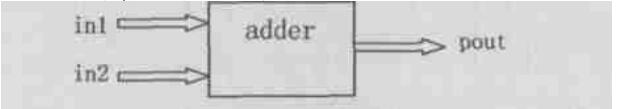

| 1769-PB2 为了测试本文提出的设计方案的正确性和有效性,在设计过程中选取了一些常用的数字电路系统来比较C源程序和VHDL目标程序的功能一致性。例如对于一个无控制端口的加法器电路,其电路示意图见图2

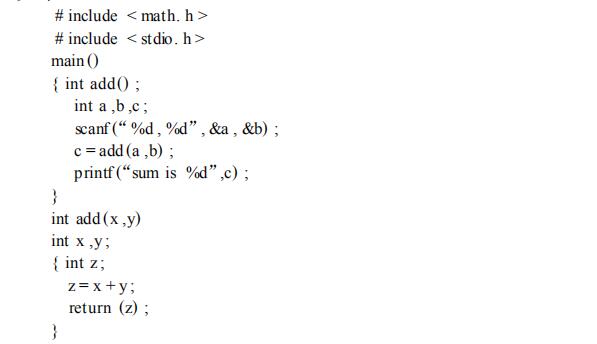

该加法器不带任何控制端口,有两个输入端口in1和in2,一个输出端口pout,它们的类型皆为位向量。当输入信号中有任何一个或者两个都发生变化时,进程就要再重新执行一遍。从电路功能的角度来理解:只要在输入端有新的数据输入,那么加法器必然要重新开始工作,将新的数值相加并送到输出端口,这样不断地进行加法操作。对于加法器电路的C语言描述如下

利用本文提出的设计方案对实现加法器功能的C 语言程序进行编译转换, 得到转换后的目标程序———VHDL 程序如下:

1769-PB2 · 成就客户—我们致力于每位客户的满意和成功。

· 创业创新—我们追求对客户和公司都至关重要的创新,同时快速而高效地推动其实现。

· 诚信正直—我们秉持信任、诚实和富有责任感,无论是对内部还是外部。

· 多元共赢—我们倡导互相理解,珍视多元性,以全球视野看待我们的文化。

--------------------

联系人:欧工

手机:18030229050

电话:0592-5709821

QQ 3151326358

邮箱 3151326358@qq.com

1769-PB2

140ACI04000 140DDM39000 140DDM69000 140DDO15310 140DDO35300

140DDO35301 140DDO35310 140DDO36400 140DDO84300 140DDO88500

140DII33000 140DIO33000 140DRA84000 140DRC83000 140DSI35300

140DVO85300 140EDK77100 140EHC10500 140EHC20200 140EIA92100

140ERT85410 140ESI06210 140HLI34000 140MSB10100

140MSC10100 140NOA61100 140NOE31100 140NOE35100

140NOE51100 140NOE55100 140NOE77101 140NOE77110

140NOL91100 140NOL91120 140NOM21100 140NOM21200 140NOM25200

140SHS94500 140XBE10000 140XBP00200 140XBP00300

140XBP00400 140XBP00600 140XBP01000 140XBP01600

140XCA10206 140XCA10215 140XCA71703 140XCA71700

140XCA71709 140XCP20000 140XCP40100 140XCP40200

140XCP50000 140XCP51000 140XCP60000 140XCP90000

140XSM00200 140XSM01000 140XTS00100 140XTS00200

140XTS00203 140XTS00206 140XTS00209 140XTS00212

140XTS00500 140XTS01203 140XTS01206 140XTS01209

140XTS01212 140XTS10206 140XTS10215 140XTS33200

140ACO02000 140ACO13000 140AII33000 140AII33010

140AIO33000 140AMM09000 140ARI03010 140ATI03000

140AVI03000 140AVO02000 140CFA04000 140CFB03200

140CFC03200 140CFD03200 140CFE03200 140CFG01600

140CFH00800 140CFI00800 140CFJ00400 140CFK00400 140CFU00600

140CFU08000 140CFU40000 140CFX00110 140CFX00210

140CHS11000 140CHS21000 140CHS32000 140CPS11100

|